Desarrollo: 1989-2000

En 1989, HP pensó que las arquitecturas RISC (Reduced InstructionSet Computing) estaban estancadas en una instrucción por ciclo. Los investigadores de HP intentaron crear un nuevo tipo de arquitectura de procesador, que más tarde se llamó Explicitly Parallel Instruction Computing (EPIC), que permite al procesador utilizar muchas instrucciones en cada ciclo de reloj. EPIC utiliza una forma de arquitectura de palabras de instrucción muy largas (VLIW), en la que una palabra de instrucción tiene muchas instrucciones. Con EPIC, el compilador comprueba qué instrucciones pueden utilizarse al mismo tiempo, de modo que el procesador puede ejecutar las instrucciones sin necesidad de métodos complicados para ver qué instrucciones utilizar al mismo tiempo. El objetivo de esta idea es permitir una mejor inspección del código en el momento de la compilación para comprobar si hay oportunidades adicionales de ejecuciones múltiples a la vez, y simplificar el diseño del procesador y ahorrar electricidad al eliminar la necesidad de instrucciones de programación en tiempo de ejecución.

HP pensó que no era bueno para las empresas de sistemas empresariales individuales como HP fabricar procesadores propietarios, por lo que HP trabajó con Intel en 1994 para crear la arquitectura IA-64, realizada con las ideas de EPIC. Intel quería hacer un gran esfuerzo en la creación de IA-64 con la esperanza de que el procesador resultante fuera utilizado por la mayoría de los sistemas empresariales. HP e Intel realizaron un gran esfuerzo de diseño para fabricar el primer producto Itanium, Merced, en 1998.

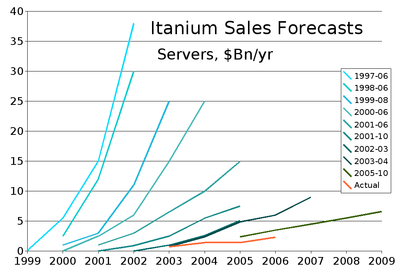

Durante su creación, Intel, HP y otros analistas de la industria pensaron que IA-64 sería muy popular en servidores, estaciones de trabajo y ordenadores de sobremesa, y que algún día sustituiría a las arquitecturas RISC y Complex Instruction Set Computing (CISC) para aplicaciones polivalentes. Compaq y Silicon Graphics dejaron de trabajar en sus arquitecturas Alpha y MIPS para pasar a la arquitectura Itanium.

Muchos grupos crearon sistemas operativos para Itanium, entre ellos Microsoft Windows, OpenVMS, Linux y tipos de UNIX como HP-UX, Solaris, Tru64 UNIX y Monterey/64 (los tres últimos nunca terminaron de funcionar con Itanium). En 1997, muchos descubrieron que la arquitectura Itanium y el compilador eran más difíciles de usar de lo que pensaban. Problemas tecnológicos como el altísimo número de transistores necesarios para las grandes palabras de instrucción y las grandes cachés.[] También hubo problemas con el proyecto, ya que las dos partes del equipo utilizaban métodos diferentes y tenían prioridades ligeramente distintas.[] Como Merced fue el primer procesador EPIC, su creación tuvo más problemas de los que el equipo había pensado. Además, el concepto EPIC requiere unas capacidades de compilación diferentes que nunca se habían creado antes, por lo que fue necesario investigar más. []

Intel anunció el nombre del procesador, Itanium, el 4 de octubre de 1999. En sólo unas horas, el nombre Itanic había sido utilizado como una broma, (una referencia al Titanic, el barco "insumergible" que se hundió en 1912 ("Itanium + Titanic = Itanic")). "Itanic" también ha sido utilizado por The Register, y otros, para decir que la multimillonaria inversión en Itanium, y la temprana demanda con ella, no significaría nada porque pensaban que Itanium iba a fracasar.

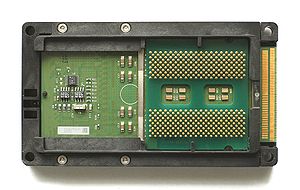

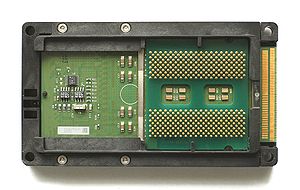

Itanium (Merced): 2001

| Itanium (Merced) |

|

|

| Producido | De junio de 2001 a junio de 2002 |

| Fabricante(s) habitual(es) | |

| Máx. Velocidad de reloj de la CPU | 733 MHz a 800 MHz |

| Velocidades del FSB | 266 MT/s |

| Conjunto de instrucciones | Itanium |

| Número de núcleos | 1 |

| Caché L2 | 96 KB |

| Caché L3 | 2 o 4 MB |

| Enchufe(s) | |

| Nombre del núcleo | |

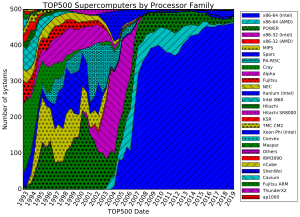

Cuando Itanium salió al mercado en junio de 2001, su rendimiento no era superior al de los procesadores RISC y CISC de la competencia. Itanium compitió con sistemas de bajo consumo (principalmente sistemas de 4 CPU y pequeños) con servidores basados en procesadores x86, y con los de alto consumo, como con la arquitectura POWER de IBM y la arquitectura SPARC de Sun Microsystems. Intel cambió Itanium para trabajar con el negocio de la alta potencia y la informática HPC, intentando copiar el éxito del mercado de x86 (es decir, 1 arquitectura, muchos proveedores de sistemas). El éxito de la primera versión del procesador consistió únicamente en sustituir a PA-RISC en los sistemas de HP, a Alpha en los de Compaq y a MIPS en los de SGI, pero IBM también fabricó un superordenador basado en esta arquitectura. El POWER y el SPARC fueron fuertes, y la arquitectura x86 creció más en el espacio empresarial, debido a la facilidad de escalado y a la gran base de instalación.

Sólo se vendieron unos pocos miles de sistemas que utilizaban el primer procesador Itanium, Merced, debido a su menor rendimiento, su elevado coste y la escasez de software hecho con Itanium. Intel vio que Itanium necesitaba más software nativo para funcionar bien, por lo que fabricó miles de sistemas para que los proveedores de software independientes les ayudaran a crear software Itanium. HP e Intel sacaron al mercado el segundo procesador Itanium, Itanium 2, un año después.

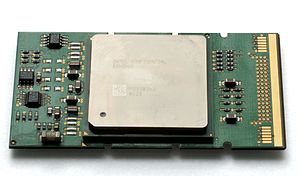

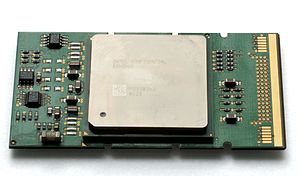

Itanium 2: 2002-2010

| Itanium 2 (McKinley) |

|

|

| Producido | De 2002 a 2010 |

| Diseñado por | Intel |

| Fabricante(s) habitual(es) | |

| Máx. Velocidad de reloj de la CPU | 900 MHz a 2,53 GHz |

| Conjunto de instrucciones | Itanium |

| Número de núcleos | 1, 2, 4 u 8 |

| Caché L2 | 256 KB en Itanium2

256 KB (D) + 1 MB(I) o 512 KB (I) en (Itanium2 serie 9x00) |

| Caché L3 | 1,5-32 MB |

| Enchufe(s) | - PAC611

- FC-LGA6 (LGA1248) (serie Itanium 9300)

|

| Nombre del núcleo | - McKinley

- Madison

- Hondo

- Deerfield

- Montecito

- Montvale

- Tukwila

- Poulson

|

El procesador Itanium 2 fue lanzado en 2002, para servidores empresariales y no para toda la informática de alta potencia. La primera versión de Itanium 2, cuyo nombre en clave es McKinley, fue creada por HP e Intel. Corregía muchos de los problemas del primer procesador Itanium, causados principalmente por un mal subsistema de memoria. McKinley tenía 221 millones de transistores (25 millones de ellos eran para la lógica), y medía 19,5 mm por 21,6 mm (421 mm 2) y fue creado con un proceso de diseño de 180 nm, y un proceso CMOS con 6 capas de aluminio.

En 2003, AMD lanzó el Opteron, que implementó la primera arquitectura x86-64 (llamada entonces AMD64). Opteron tuvo mucho más éxito porque era una actualización fácil de x86. Intel implementó x86-64 en sus procesadores Xeon en 2004.

Intel lanzó un nuevo procesador Itanium 2, cuyo nombre en clave era Madison, en 2003. Madison utilizaba un proceso de 130 nm y fue la base de todos los nuevos procesadores Itanium hasta junio de 2006.

En marzo de 2005, Intel anunció que estaba trabajando en un nuevo procesador Itanium, cuyo nombre en clave era Tukwila, que saldría a la venta en 2007. Tukwila tendría 4 núcleos de procesamiento y sustituiría el bus Itanium por una nueva interfaz de sistema común, que también utilizaría un nuevo procesador Xeon. Ese mismo año, Intel cambió la fecha de lanzamiento de Tukwila a finales de 2008.

En noviembre de 2005, los mayores fabricantes de servidores Itanium colaboraron con Intel y muchos proveedores de software para crear la Itanium Solutions Alliance, con el fin de promover la arquitectura y acelerar la portabilidad del software. La Alianza afirma que sus miembros invertirán 10.000 millones de dólares en soluciones Itanium para el final de la década.

En 2006, Intel presentó Montecito (comercializado como la serie Itanium 2 9000), un procesador de dos núcleos que tenía aproximadamente el doble de rendimiento y un 20% menos de consumo de energía.

Intel lanzó la serie Itanium 2 9100, cuyo nombre en clave era Montvale, en noviembre de 2007. En mayo de 2009, el lanzamiento de Tukwila, el sucesor de Montvale, se modificó de nuevo, con un lanzamiento a los OEM previsto para el primer trimestre de 2010.

Itanium 9300 (Tukwila): 2010

El procesador de la serie Itanium 9300, cuyo nombre en clave es Tukwila, salió al mercado el 8 de febrero de 2010, con mayor rendimiento y cantidad de memoria.

Tukwila utiliza un proceso de 65 nm, tiene entre dos y cuatro núcleos, hasta 24 MB de caché de CPU, tecnología Hyper-Threading y nuevos controladores de memoria. También cuenta con corrección de datos de doble dispositivo, que ayuda a solucionar los problemas de memoria. Tukwila también cuenta con Intel QuickPath Interconnect (QPI) para sustituir la arquitectura de bus Itanium. Tiene un ancho de banda máximo para el procesador interno de 96 GB/s y un ancho de banda máximo para la memoria de 34 GB/s. Con QuickPath, el procesador cuenta con controladores de memoria integrados, que controlan la memoria utilizando interfaces QPI para comunicarse con otros procesadores y concentradores de E/S. QuickPath también se utiliza con los procesadores Intel que emplean la arquitectura Nehalem, por lo que Tukwila y Nehalem podrían utilizar los mismos conjuntos de chips. Tukwila incorpora cuatro controladores de memoria, cada uno de los cuales admite varios módulos DIMM DDR3 a través de un controlador de memoria independiente, de forma similar al procesador Nehalem Xeon con nombre de código Beckton.

Itanium 9500 (Poulson): 2012

| | Este artículo necesita ser actualizado. Puedes ayudar a Wikipedia actualizándolo. (Marzo 2014) |

El procesador de la serie Itanium 9500, cuyo nombre en clave es Poulson, es el sucesor de Tukwila y fue lanzado el 8 de noviembre de 2012. Intel afirma que se salta la tecnología de proceso de 45 nm y utiliza en su lugar la tecnología de proceso de 32 nm; cuenta con 8 núcleos, tiene una arquitectura de 12 números de ancho, adiciones de multihilo y nuevas instrucciones para el paralelismo, incluida la virtualización. El tamaño de la caché L3 de Poulson es de 32 MB. El tamaño de la caché L2 es de 6 MB, 512 I KB, 256 D KB por núcleo. El tamaño de Poulson es de 544 mm², menos que el de Tukwila (698,75 mm²).

En la ISSCC 2011, Intel presentó una ponencia titulada "A 32nm 3.1 Billion Transistor 12-Wide-Issue Itanium Processor for Mission Critical Servers". Dado el historial de Intel de compartir detalles sobre los microprocesadores Itanium en la ISSCC, lo más probable es que esta ponencia se refiera a Poulson. El analista David Kanter especula que Poulson utilizará una nueva arquitectura, con una forma más avanzada de multihilo que utiliza hasta dos hilos, para mejorar el rendimiento en trabajos de un solo hilo y de varios. La nueva información se dio a conocer en la conferencia Hot Chips.

La nueva información afirma que hay mejoras en el multithreading, mejoras en la fiabilidad (Instruction Replay RAS) y algunas instrucciones nuevas (prioridad de hilos, instrucción de enteros, pre-fetching de caché, sugerencias de acceso a datos).

En la notificación de cambio de producto (PCN) 111456-01 de Intel, se enumeraban 4 modelos de CPU de la serie Itanium 9500, que se eliminaron en una versión revisada del documento. Las piezas se incluyeron posteriormente en la base de datos de hojas de datos de declaración de materiales (MDDS) de Intel. Posteriormente, Intel publicó el manual de referencia de Itanium 9500.

Los modelos son:

| Número de procesador | Frecuencia |

| 9520 | 1,73 GHz |

| 9540 | 2,13 GHz |

| 9550 | 2,4 GHz |

| 9560 | 2,53 GHz |