Una interrupción es cuando un microprocesador hace algo que no se le ha ordenado debido a cosas que suceden fuera de lo que se supone que debe hacer el programa. Las interrupciones suelen producirse porque el procesador recibe una señal del hardware, pero también pueden provenir del software que se ejecuta junto con el programa. Entre las muchas cosas que pueden causar interrupciones están la pulsación de teclas en un teclado, la activación del temporizador incorporado, la realización de una transferencia de datos o cualquier otro evento que necesite una acción del procesador de inmediato. Las interrupciones pueden ocurrir en cualquier momento mientras el procesador está ejecutando un programa, sin importar en qué parte del código fuente del programa se encuentre.

¿Qué es una interrupción? (definición ampliada)

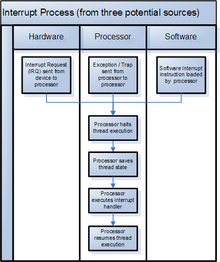

En términos sencillos, una interrupción es un mecanismo por el cual un dispositivo o una condición solicita la atención inmediata de la CPU. En lugar de que el procesador continúe ejecutando instrucciones secuenciales, detiene temporalmente la ejecución normal, guarda su estado y ejecuta una rutina específica llamada Manejador de Interrupciones o ISR (Interrupt Service Routine). Cuando el ISR termina, la CPU restaura el estado guardado y retoma la ejecución del programa interrumpido.

Tipos principales de interrupciones

- Interrupciones por hardware (asíncronas): Generadas por dispositivos externos (teclado, disco, tarjeta de red, temporizadores). Suelen llegar a través de controladores o controladores de interrupciones como PIC o APIC.

- Interrupciones por software (síncronas): Provocadas por instrucciones que generan llamadas al sistema, traps o solicitudes explícitas del programa (por ejemplo, una llamada al sistema operativo).

- Excepciones: Condiciones detectadas por la CPU durante la ejecución de instrucciones (por ejemplo, división por cero, fallo de página, instrucción ilegal). Aunque a veces se agrupan con las interrupciones, son eventos sincronizados con la ejecución de instrucciones.

- Non-maskable Interrupt (NMI): Interrupciones de alta prioridad que no se pueden enmascarar (deshabilitar). Se usan para errores críticos de hardware que requieren atención inmediata.

- Interrupciones enmascarables: Pueden ser habilitadas o deshabilitadas por el software (por ejemplo, con banderas de interrupción en la CPU).

- Edge-triggered vs level-triggered: Dependiendo si se detecta el flanco de la señal (borde) o el nivel sostenido; esto afecta la forma en que el controlador valora y maneja la señal.

Cómo funciona el manejo de interrupciones (flujo básico)

- Generación: Un dispositivo o el propio procesador genera la señal de interrupción.

- Detección y aceptación: La CPU reconoce la interrupción (según prioridades y mascaras) y completa la instrucción en curso si es necesario.

- Guardar contexto: La CPU guarda el contexto (registros, contador de programa, flags) en la pila o en áreas reservadas para poder reanudar después.

- Vectorización: Se localiza la dirección de la ISR mediante una tabla de vectores o descriptor de interrupción.

- Ejecutar ISR: La rutina de servicio se ejecuta para atender el evento (leer datos, limpiar banderas, iniciar DMA, etc.).

- Restaurar contexto: Al terminar, la CPU restaura el contexto guardado.

- Retomar ejecución: La CPU continúa con la instrucción o el hilo interrumpido.

Elementos clave y conceptos relacionados

- ISR (Interrupt Service Routine): Código que atiende la interrupción. Debe ser breve y eficiente para minimizar la latencia.

- Vector de interrupción: Identificador que apunta a la dirección del ISR correspondiente.

- Controlador de interrupciones: Componente (hardware) que arbitra muchas señales de interrupción y las presenta ordenadas y priorizadas a la CPU (ej.: PIC, APIC).

- Contexto: Conjunto de registros y estado que deben preservarse para reanudar correctamente la ejecución.

- Latencia de interrupción: Tiempo desde que se genera la interrupción hasta que la ISR comienza a ejecutarse. Es crítico en sistemas en tiempo real.

- Máscara de interrupciones: Mecanismo para deshabilitar temporalmente ciertas interrupciones mientras se realizan secciones críticas.

- Interrupciones anidadas: Cuando una ISR puede a su vez ser interrumpida por otra de mayor prioridad; requiere manejo cuidadoso del contexto y prioridades.

Ejemplos prácticos

- Pulsar una tecla en un teclado — el controlador envía una interrupción para que el sistema operativo lea la tecla y la procese.

- Temporizador interno — genera interrupciones periódicas para planificar tareas (scheduling) o para mantener la hora del sistema (temporizador incorporado).

- Controladores de disco o red — notifican al procesador que una operación de E/S ha terminado para procesar los datos (datos).

- Instrucción ilegal o división por cero — la CPU genera una excepción para que el sistema pueda manejar el error o terminar el proceso.

- Llamadas al sistema (system calls) — instrucciones de software que provocan una transición controlada al kernel para ejecutar servicios privilegiados.

Interrupciones vs sondeo (polling)

En lugar de usar interrupciones, algunos sistemas consultan periódicamente (polling) a los dispositivos para saber si necesitan atención. Comparación rápida:

- Interrupciones: Más eficientes en CPU y reactivas; permiten que la CPU haga otras tareas hasta que ocurra el evento.

- Polling: Sencillo de implementar pero consume CPU y puede introducir latencia si los sondeos son poco frecuentes.

Buenas prácticas y consideraciones

- Hacer las ISRs lo más cortas posible: delegar trabajo pesado a hilos o procesos en el contexto de usuario o a tareas diferidas (bottom halves, workqueues).

- Gestionar adecuadamente las prioridades para evitar inanición de interrupciones críticas.

- Proteger secciones críticas con mascaras o mecanismos de sincronización para evitar inconsistencias al guardar/restaurar contexto.

- Medir y optimizar la latencia en sistemas en tiempo real.

- En sistemas multiprocesador, usar controladores y arquitecturas (APIC) que soporten distribución y afinidad de interrupciones.

Resumen

Las interrupciones son un mecanismo fundamental que permite a los microprocesadores reaccionar rápidamente a eventos internos y externos sin desperdiciar ciclos de CPU en espera activa. Conocer los tipos de interrupciones, cómo se manejan y las implicaciones de diseño (latencia, prioridades, contextos) es esencial para diseñar sistemas operativos, controladores y aplicaciones eficientes y fiables.